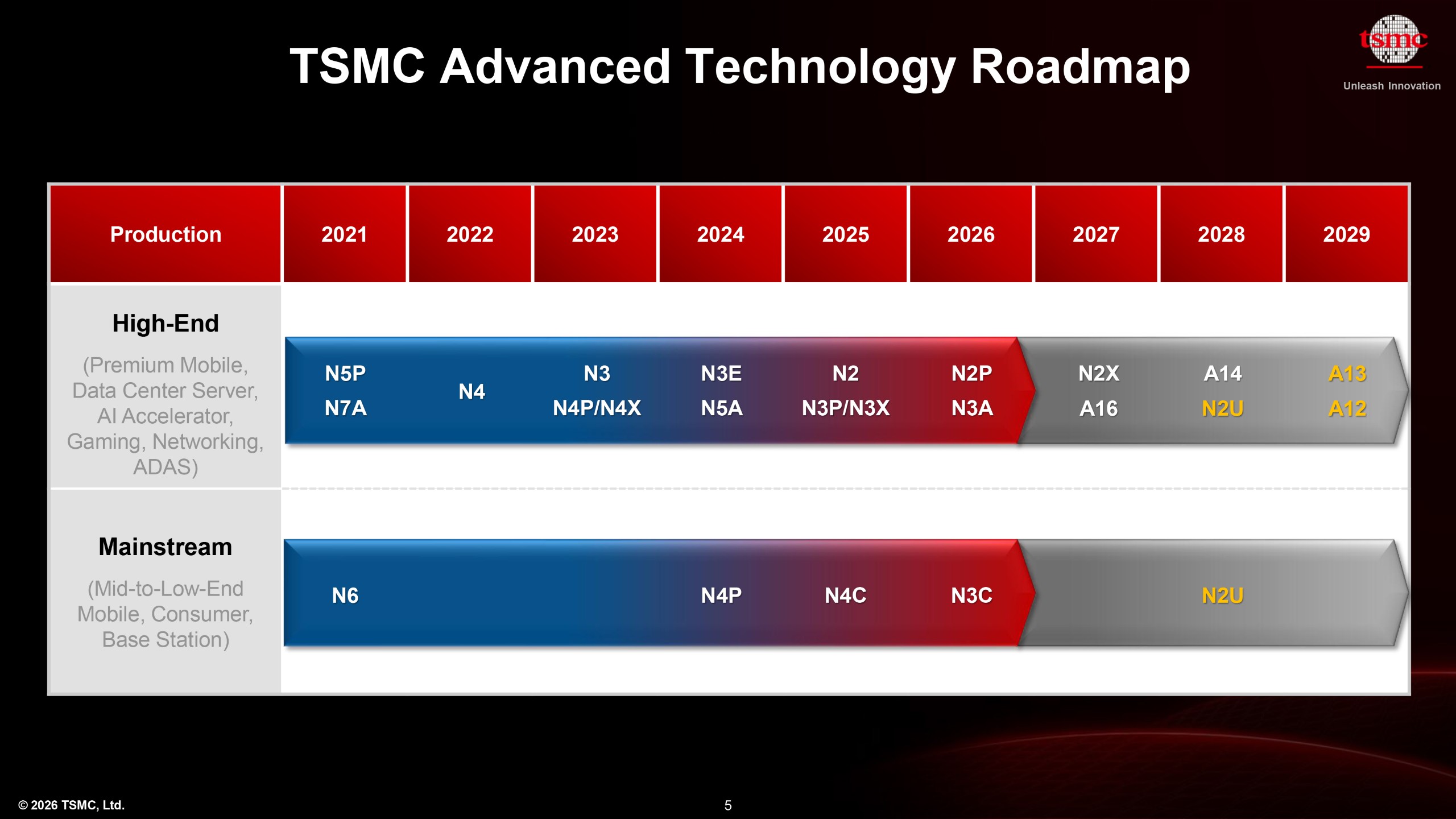

Durante o Simpósio de Tecnologia da América do Norte de 2026, a TSMC detalhou sua estratégia para o final da década. A gigante das fundições planeja introduzir os nós de 1,3 nm (A13) e 1,2 nm (A12) em 2029. O diferencial desta estratégia é a decisão de adiar o uso das máquinas EUV de Alta Abertura Numérica (High-NA) da ASML, cujo custo é atualmente considerado proibitivo.

A equipe de engenharia da TSMC focará em estender a vida útil da litografia EUV atual, utilizando técnicas de escalonamento para entregar chips menores e mais potentes para notebooks, smartphones e infraestrutura de IA.

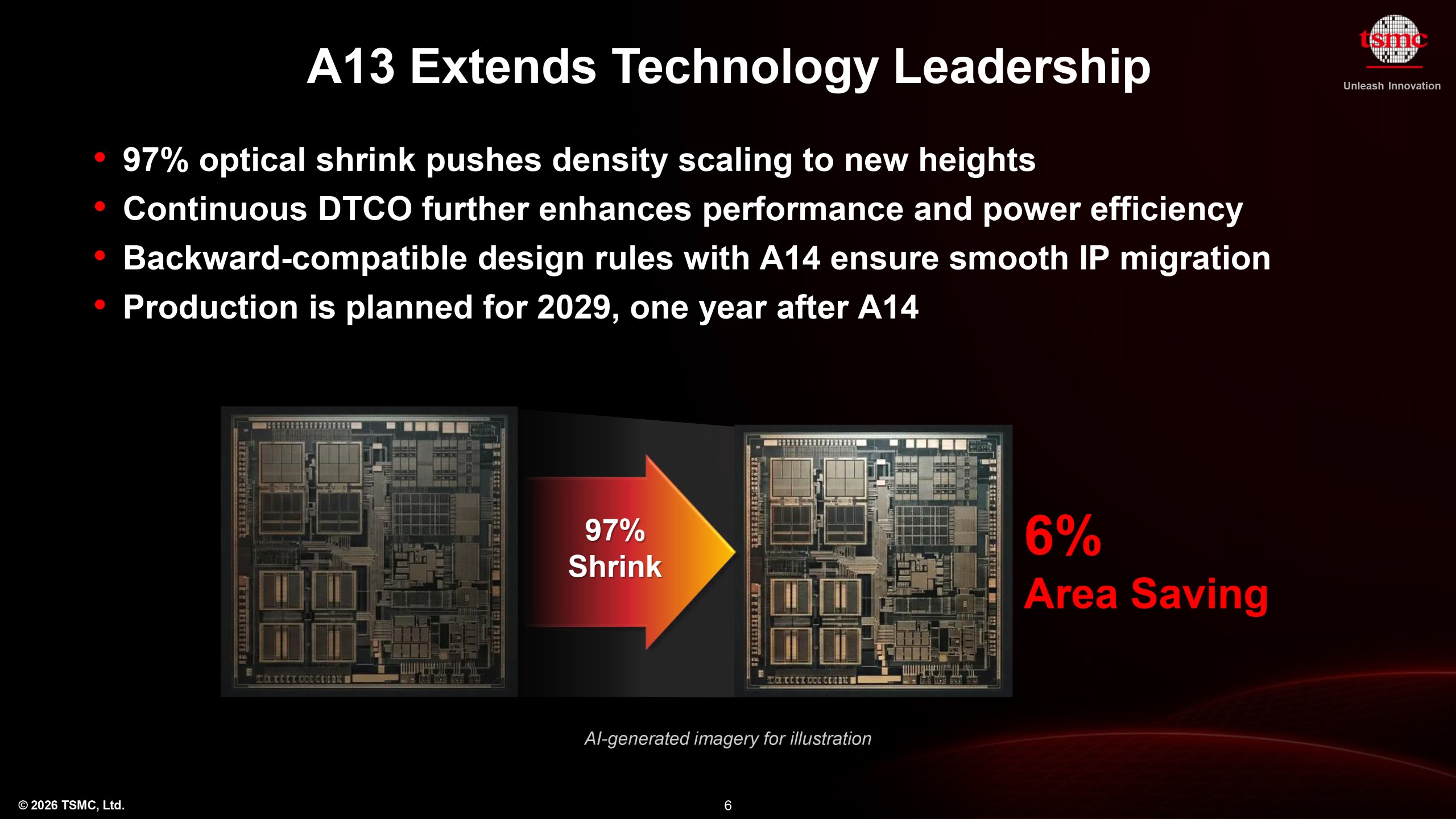

Evolução dos nós do A14 ao A12

A transição para a era Angstrom seguirá um cronograma de refinamentos sucessivos para garantir eficiência e desempenho:

- Nó A13 (1,3 nm): Previsto para 2029, é uma versão otimizada do nó A14 (1,4 nm). Oferece uma redução de área de 6%, permitindo designs mais compactos e eficientes, com retrocompatibilidade para facilitar a migração de projetos.

- Nó A12 (1,2 nm): Também planejado para 2029, foca na entrega de energia. Utilizará a tecnologia Super Power Rail, que move a rede de distribuição de energia para a parte traseira do chip, liberando espaço para mais transistores e melhorando o perfil térmico.

- Nó N2U (2 nm): Uma opção equilibrada prevista para 2028, oferecendo até 10% de redução no consumo de energia ou ganhos de velocidade de até 4% em relação ao processo N2P.

Inovações em encapsulamento 3D e fotônica

Além da redução dos transistores, a TSMC aposta em tecnologias de empilhamento para sustentar a IA Agêntica e datacenters de alto desempenho.

| Tecnologia | Previsão | Impacto Principal |

| COUPE (Óptica Co-embalada) | 2026 | Redução de latência de 10 vezes e dobro de eficiência energética. |

| CoWoS (14 retículos) | 2028 | Integração de 10 chips de computação e 20 stacks de HBM. |

| SoIC A14-para-A14 | 2029 | Densidade de E/S 1,8 vez maior que a geração atual de chips 3D. |

| SoW-X (40 retículos) | 2029 | Formatos massivos para supercomputação de próxima geração. |

Estratégia de custo e eficiência em litografia

A relutância da TSMC em adotar imediatamente o High-NA EUV é uma manobra financeira para manter o custo total de propriedade competitivo. Segundo Kevin Zhang, vice-presidente sênior da empresa, os benefícios de escalabilidade do nó A14 já são substanciais com as ferramentas atuais.

Essa postura permite que a TSMC continue expandindo fábricas globais enquanto aguarda a maturação das ferramentas de litografia de próxima geração. Para o setor de hardware, isso garante que a evolução para chips de 1,2 nm ocorra de forma estável, mantendo a viabilidade econômica para a produção de processadores de alto desempenho.

Fonte da matéria: WCCFtech

Siga o TecLab em todas as mídias: linktr.ee/rbuass

Galindowie • 23 de abril de 2026 às 09:48 GMT-3

0 comentários