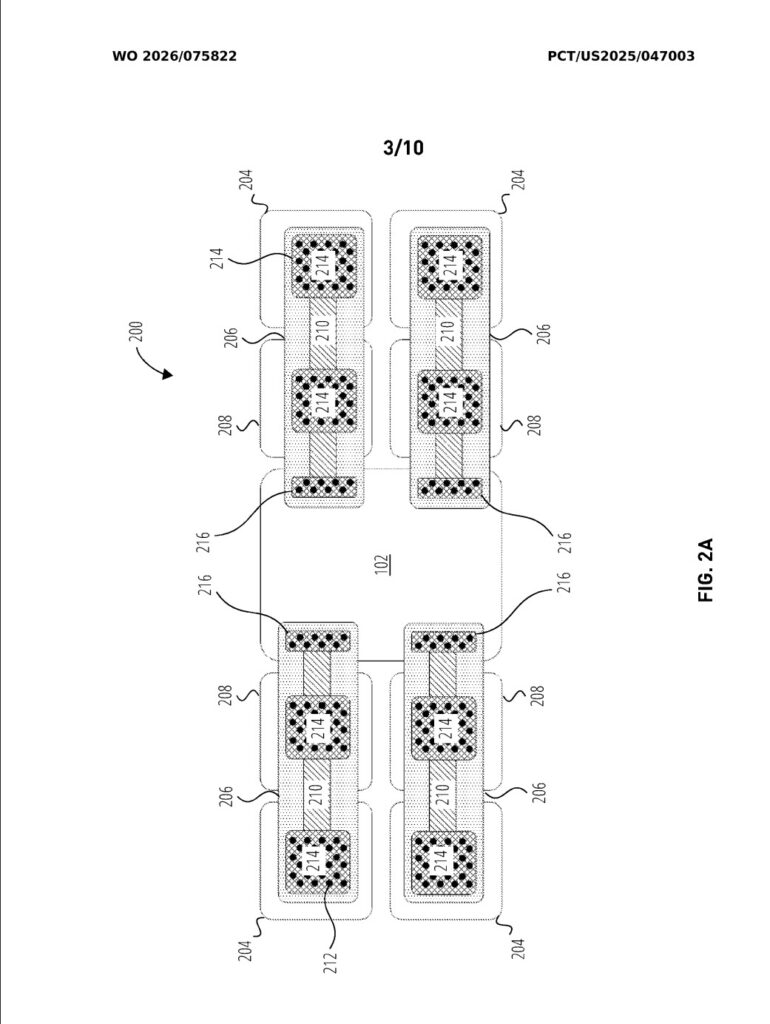

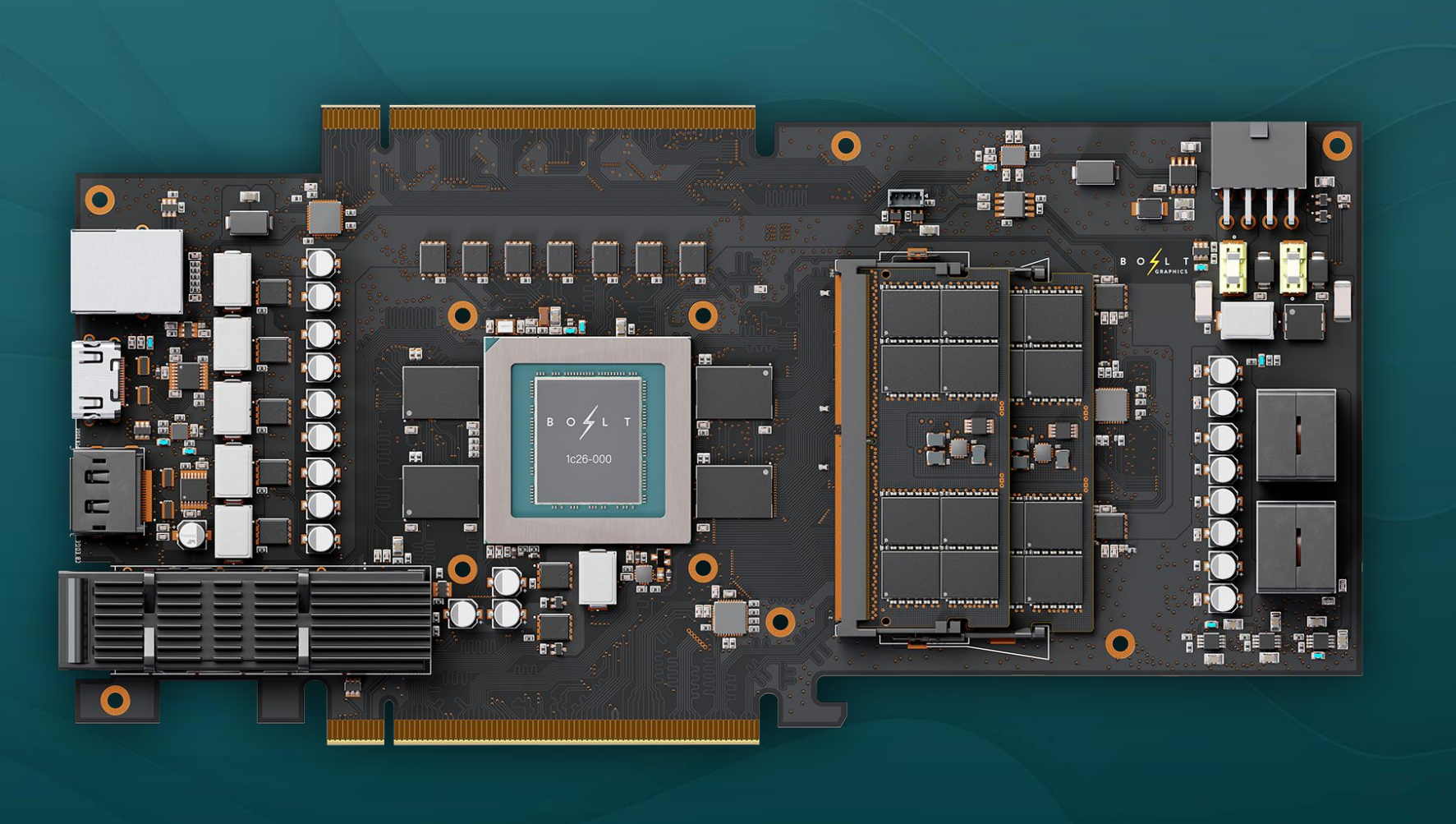

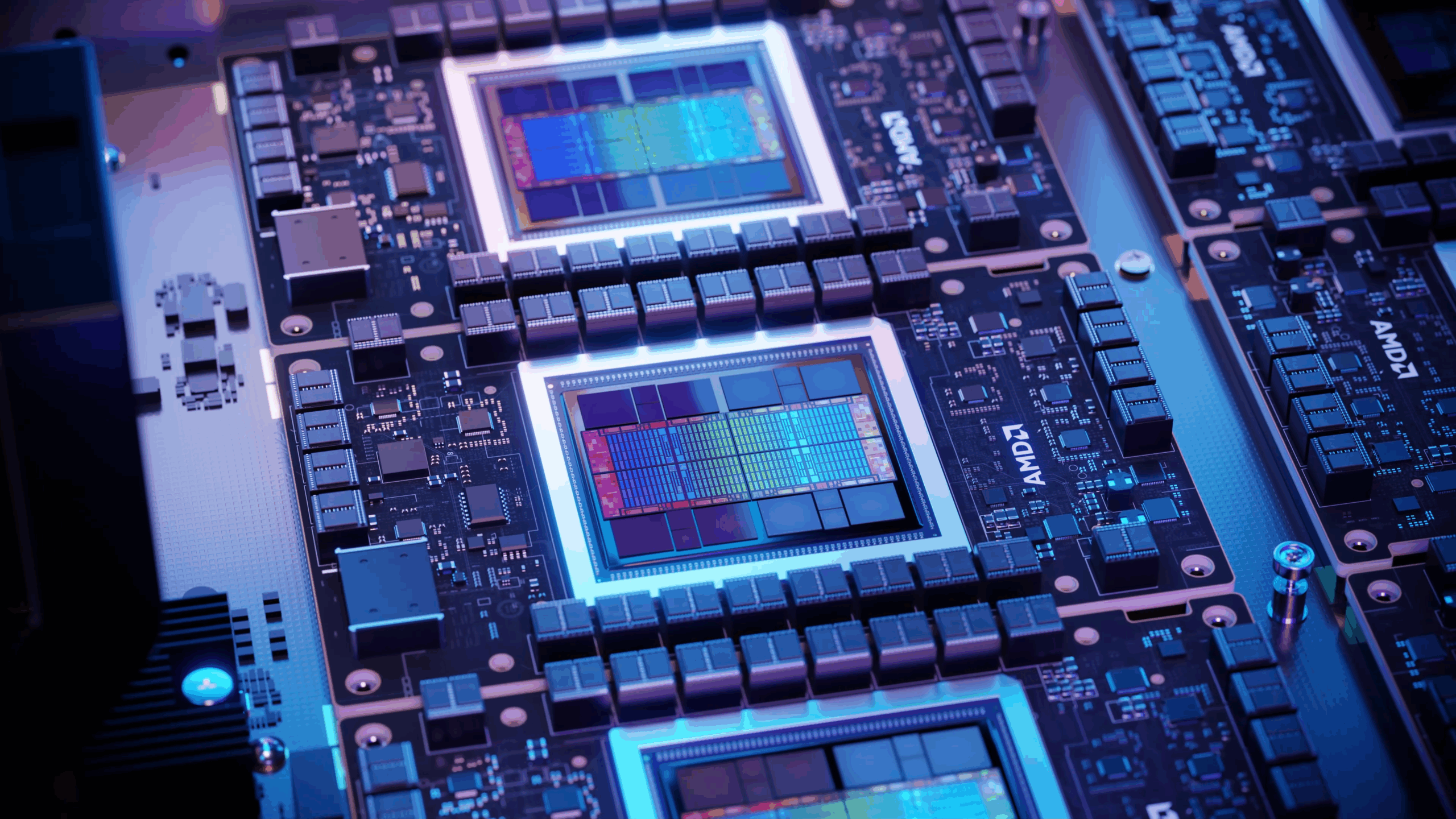

Uma nova patente da OpenAI, intitulada “Conexão não adjacente de chiplets de memória de alta largura de banda, chiplets de E/S e chiplets de computação por meio de pontes lógicas embutidas”, revelou planos ambiciosos da organização para hardware personalizado. O projeto propõe superar as limitações físicas atuais de encapsulamento, permitindo que um único chiplet de computação seja cercado por até 20 pilhas de memória HBM, um salto massivo em relação ao limite atual de oito pilhas das arquiteturas convencionais.

A inovação central reside no uso de Pontes Lógicas Incorporadas (EBPs). Atualmente, o padrão JEDEC exige que a memória HBM esteja adjacente ao chiplet principal, com conexões metálicas limitadas a 6 mm. A solução da OpenAI estende essa distância para até 16 mm, possibilitando um design muito mais denso e expansível.

Tecnologia de pontes e o papel da Intel

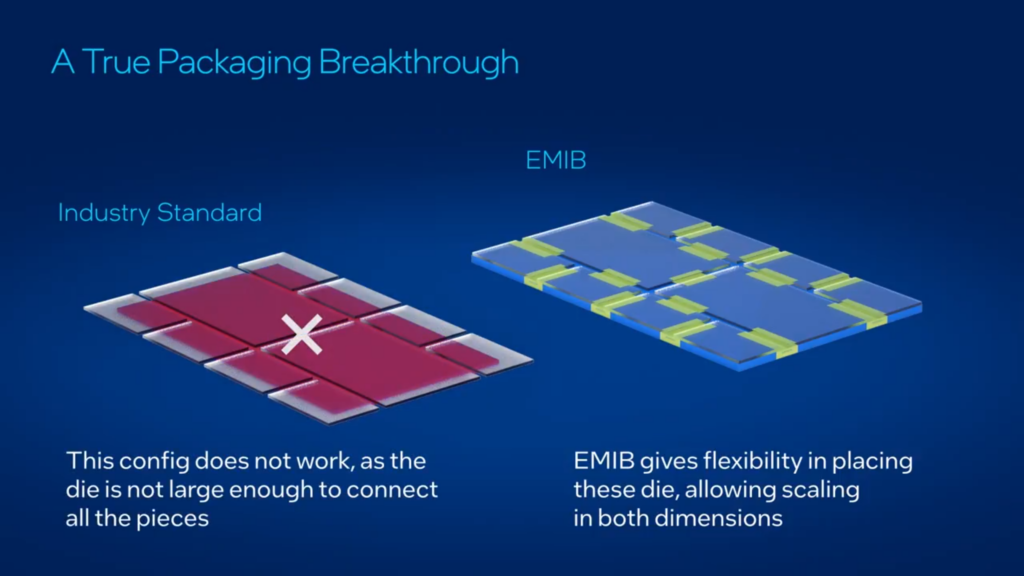

A abordagem da OpenAI guarda semelhanças técnicas profundas com a tecnologia EMIB (Embedded Multi-Interconnect Bridge) da Intel. Essa solução de encapsulamento 2.5D utiliza pequenas pontes embutidas no substrato para conectar chiplets, oferecendo vantagens críticas:

- Escalabilidade: Permite expandir o chip além dos limites de retículo dos interposers tradicionais.

- Custo-benefício: É uma alternativa mais econômica e simples às camadas base de silício completas.

- Funcionalidade: As pontes podem atuar como controladores para as pilhas HBM ou como interfaces físicas (PHY) de alta velocidade, seguindo o padrão UCIe (Universal Chiplet Interconnect Express).

Por que 20 módulos HBM?

Modelos de linguagem de larga escala e sistemas de IA Agêntica exigem acesso ultrarrápido a volumes massivos de dados. Ao integrar 20 módulos de memória, a OpenAI busca eliminar o gargalo de largura de banda que limita o treinamento e a inferência de modelos de próxima geração.

| Recurso | Padrão Atual (Ex: H100 / B200) | Patente da OpenAI (EBP) |

| Módulos HBM | 4 a 8 pilhas | Até 20 pilhas |

| Distância de Conexão | Máximo de 6 mm | Até 16 mm |

| Tipo de Ponte | Interposer de Silício / Fios Metálicos | Pontes Lógicas Embutidas (Estilo EMIB) |

| Interface D2D | Proprietária / Diversas | Padrão UCIe |

Futuro dos chips personalizados

A publicação desta patente reforça os rumores de que a OpenAI busca reduzir sua dependência exclusiva da NVIDIA ao projetar seu próprio silício. O uso de uma tecnologia similar ao EMIB sugere uma possível colaboração futura com a Intel Foundry para a fabricação desses chips, aproveitando a infraestrutura de encapsulamento avançado nos EUA.

Com a capacidade de memória significativamente ampliada, esses novos chips poderiam processar contextos de dados muito maiores e executar modelos de IA com uma eficiência energética e computacional sem precedentes no mercado de 2026.

Fonte da matéria: WCCFtech

Siga o TecLab em todas as mídias: linktr.ee/rbuass

Galindowie • 22 de abril de 2026 às 12:06 GMT-3

0 comentários